Utviklingen av prosessorteknologi går med rykk og napp. Intel lanserte i fjor mikroarkitekturen Core, som regnes som ble regnet som en stor oppgradering i forhold til arkitekturen som ble brukt av blant annet Pentium 4.

Men i går offentliggjorde selskapet planer for to nye oppgraderinger av arkitekturen, som til sammen vil innføre langt flere endringer i designet enn det Core gjorde. Den første av disse vil innføres med prosessorfamilien Penryn, som skal lanseres til høsten.

En lang rekke nyheter skal til sammen gi store forbedringer - både når det gjelder ytelse og strømforbruk. Her er hva som skal skje:

Med lanseringen av Penryn tar Intel i bruk 45 nanometers prosessteknologi. Dette gir brikker med mindre transistorer og dermed plass til flere transistorer. Selskapet skal innen slutten av 2008 ha fire fabrikker som kan lage slike brikker. Foreløpig har selskapet femten 45 nanometers produkter under utvikling.

Det vil i første omgang lanseres seks prosessorklasser i Penryn-familien. Dette inkluderer prosessorer med to og fire kjerner til stasjonære PC-er og med to kjerner til bærbare PC-er. Disse vil selges under Intel Core-varemerket. I tillegg kommer det nye Xeon-prosessorer med to og fire kjerner.

Intel opplyser at Penryn-baserte Core 2-prosessorer med fire kjerne vil være utstyrt med 820 millioner transistorer, mens den sentrale silisiumdelen av de tokjernede prosessorene vil dekke et areal på 107 kvadratmillimeter, noe som skal være 25 prosent mindre enn dagens tilsvarende produkter. Samtidig skal effektbehovet til brikkene ikke være høyere enn med dagens prosessorer.

De mobile Penryn-brikkene vil ta i bruk en strømstyringsteknikk som Intel kaller Deep Power Down Technology. Denne skal redusere effekten til prosessorer under stilleperioder, noe som skal eliminere problemet med lekkasjestrømmer internt i transistorene. For brukeren skal dette betyr lenger batteritid.

Mobile Penryn-prosessorer skal også få en forbedret utgave av Intels Dynamic Acceleration Technology. Teknologien vil oppdage når bare én av kjernene er aktiv og øke klokkehastigheten til denne mens den andre hviler. Nettopp fordi den andre kjernen hviler, kan dette gjøres uten at det effektnivå må økes. Dette er nyttig dersom brukeren benytter programvare med bare én tråd.

Med Penryn vil Intel også innføre en ny generasjon av Streaming SIMD Extensions (SSE). SSE4 skal være den største utvidelsen siden den originale SSE-arkitekturen ble innført. Dette skal gi høyere ytelse til programvare for blant annet foto- og videoredigering.

Den generelle mikroarkitekturen skal dessuten optimaliseres til å kunne utføre flere instruksjoner per klokkesyklus enn tidligere. Dessuten skal Intels virtualiseringsteknologi forbedres, slik at transisjonstidene reduseres med mellom 25 og 75 prosent, lover Intel. Dette skal ikke kreve endringer i dagens programvare.

Den nye arkitekturen skal også åpne for bruk av høyere klokkehastigheter - i hvert fall høyere enn 3 GHz. Dessuten tar prosessorene i bruk en ny divisjonsmetode som kalles Radix 16, som skal doble divisjonshastigheten i forhold til dagens teknikker.

Det lokale prosessorminnet, gjerne kalt cache, vil økes med inntil 50 prosent i nivå 2 (L2). Tokjernede Penryn-brikker vil leveres med inntil 6 MB L2-cache, mens firekjernede vil kunne leveres med det dobbelte. Cache-minne tar mye plass på brikken og er blant de komponentene som tjener mye på at transistorstørrelsen reduseres.

Dessuten innfører Intel det selskapet kalles en Unique Super Shuffle Engine. Denne skal kunne utføre stokking av en hele bredden til en 128 bits buffer i løpet av én klokkesyklus. Denne funksjonaliteten vil utnyttes av mange nyere SSE-instruksjoner og vil bidra til høyere ytelse knyttet til blant annet multimedia.

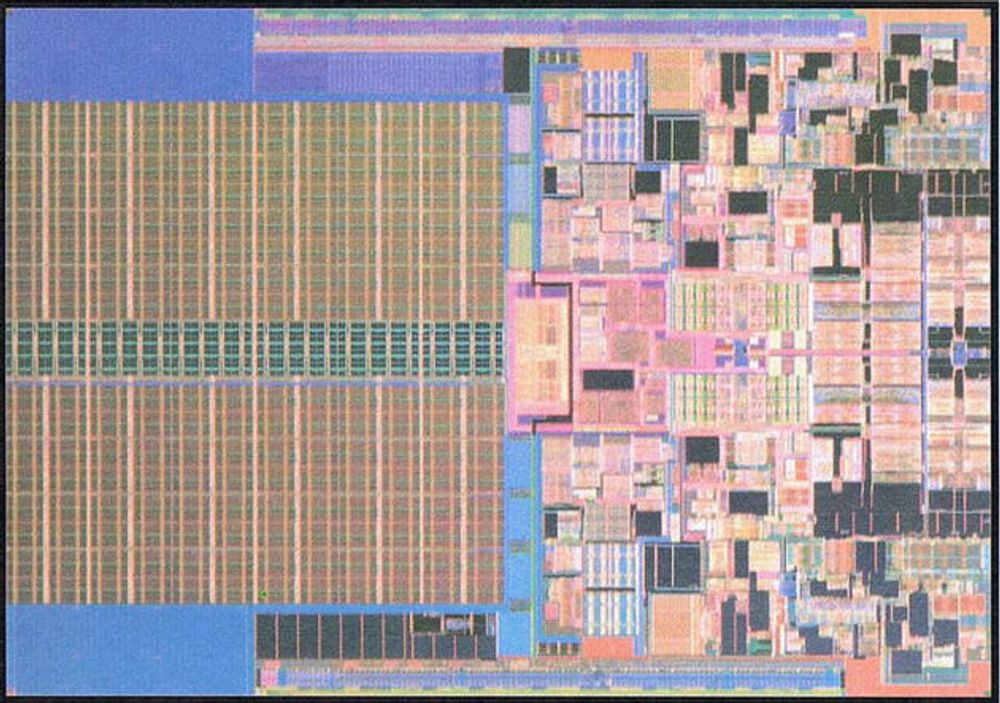

Silisium-brikken i en Intel Penryn

I løpet av 2008 vil Intel innføre enda en ny mikroarkitektur, Nehalem. Denne vil bringe med seg enda et omfattende sett med nyheter, som både skal bidra til lavere energiforbruk og høyere ytelse.

Intel nevner blant annet dynamisk styring av kjerner, tråder, cache-minne, grensesnitt og effekt. I praksis betyr det at Intels brikkedesignere enklere vil kunne tilpasse prosessormodeller som skal dekke ulike behov, ved å plukke ganske fritt fra et stort utvalg med ingredienser.

Nehalem innfører to egenskaper som er velkjente fra AMDs løsninger. Det ene er integrert minnekontroller i selve prosessorer, noe som gir økt ytelse men mindre fleksibilitet ved innføring av nye minneteknologier. Det andre en punkt-til-punkt-forbindelser mellom prosessorene - hos AMD kjent som HyperTransport.

Intel tar igjen opp tråden med Hyper-threading, en teknikk for å utføre to instruksjonstråder på én gang i hver av kjernene. Intel droppet bruken av Hyper-threading kort tid etter at selskapet hadde lansert de første tokjernede prosessormodellene.

Nehalem skal innføre enda flere SSE4-instrusjoner, men også en utvidelse av ATA-instruksjonene. Dessuten innføres en forbedret utgave av Intels Smart Cache-teknologi, som ved hjelp av spekulativ eksekvering tvers av cache-linjene skal eliminere opphold som skyldes ujevn fordeling av oppgaver.

Intel lover også bedre system- og minnebåndbredde, ytelsesforbedringer i den dynamiske strømstyringen og muligheten for en integrert grafikkmotor i selve prosessoren. Til News.com sier Pat Gelsinger, daglig leder for Intels Digital Enterprise Group, at det spesielt er Apple som ønsker seg den sistnevnte.

Nehalem skal støtte inntil 8 kjerner per prosessor.