Et amerikansk utviklingsselskap innen halvlederkonstruksjon, Tabula, melder at de er sikret 108 millioner dollar i frisk kapital som skal brukes til å sikre volumproduksjon av en ny type programmerbar brikke.

Beløpet skal være det største et nytt halvlederselskap har fått i én omgang de siste ti årene. Det kommer i tillegg til 106 millioner dollar som Tabula har hentet i løpet av de siste åtte årene. Ifølge Wall Street Journal styrer mange investorer utenom halvledersektoren, der det kreves enormt mye kapital for i det hele tatt å komme i gang, og der risikoen for å mislykkes er svært høy.

Den nye finansieringsrunden ble ledet av Crosslink Capital og DAG Ventures, med bidrag også fra eksisterende eiere Balderton Capital, Benchmark Capital, Greylock Partners, Integral Capital og NEA, heter det i en pressemelding.

Programmerbare brikker – PLD eller «programmable logic devices» – er i dag i hovedsak av en type kjent som FPGA («field programmable gate arrays») eller feltprogrammerbare portmatriser.

Disse består av et antall logiske porter med sammenkoplinger. Betegnelsen programmerbar viser til at en brikkes logiske funksjoner kan endres, ved å rekonfigurere sammenkoplingene og samspillet mellom de logiske portene.

Produsenter av elektronisk utstyr kan følgelig bruke de samme fysiske FPGA-ene til ulike oppgaver.

Framfor å bruke dedikerte brikker, der funksjonaliteten ligger fast i selve kretsene, kan dette være kostnadseffektivt. Et eksempel er innen nettverks- og teleutstyr, der spesifikasjoner må utvikles raskt, og der det kan være mer hensiktsmessig å justere programmeringen eller konfigureringen av en masseprodusert FPGA framfor å utvikle og produsere stadig nye dedikerte brikker.

Det er flere problemer knyttet til FPGA-er i dag. Et av dem har med fysisk omfang å gjøre. De er langt større enn om man hadde realisert den samme funksjonaliteten i en dedikert brikke. For det første trenger de egen minne der konfigurasjonen deres lagres. For det andre greier man, ifølge Microprocessor Report sjelden å utnytte mer enn 75 til 80 prosent av de logiske portene. For det tredje går det bort store arealer i brikken til sammenkoplinger som aldri blir benyttet. Det er en tommeregel at arealet til sammenkoplinger øker med kvadratet av antall logiske porter. I nye FPGA-er viser det seg gjerne at mindre enn 5 prosent av sammenkoplingene faktisk brukes.

Derfor er det et ekstra stort press innen programmerbare brikker å få til løsninger der logikk kan stables i høyden, i stedet for å være begrenset til to dimensjoner.

Da vil brikkene kunne bli langt mindre, fysisk sett, og den gjennomsnittlige avstanden mellom to vilkårlig valgte logiske porter vil kunne reduseres kraftig, med den følgen at sammenkoplinger vil utgjøre en mindre del av den samlede elektronikken i kretsen. Det vil igjen kunne bety underverker for ytelse og strømforbruk.

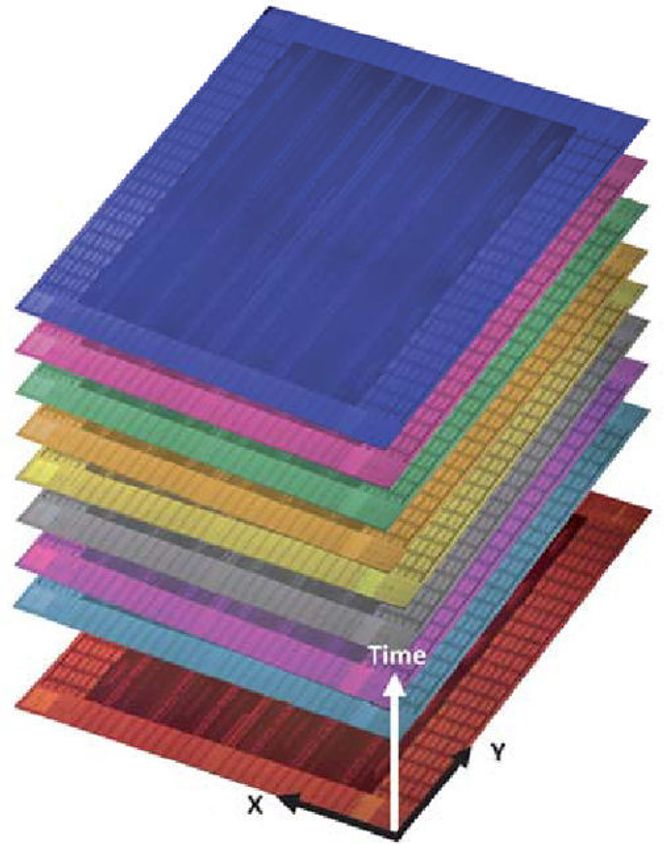

Teknologien som Tabula har utviklet, og som er kommet så langt at de ikke bare har gjennomført prøveproduksjon til utvalgte kunders tilfredshet, men også har et ferdig utviklerverktøy, løser dette ved å innføre den tredje dimensjonen ikke som fysisk høyde, men som en tidsakse.

Innen IT generelt, må dette sies å være en klassisk tilnærming, helt siden tidsdeling ble utviklet på 1960-tallet for å gi atskilte samtidige brukere inntrykk av at de disponerte hele datamaskinen hele tiden, selv om de i praksis bare hadde prosessorens oppmerksomhet en brøkdel av tiden. Operativsystemer som gir et inntrykk av å kunne kjøre flere programmer samtidig, og hypervisorer som gir et inntrykk av å kunne dele en fysisk maskin i flere virtuelle maskiner, bygger på det samme prinsippet, tidsdeling. Etter å ha brukt en eller flere klokkesykluser på én prosess, legger systemet den til side og går videre til neste.

Tabulas løsning kan følgelig oppfattes som en form for virtualiserte logiske kretser.

Deres PLD har kun ett fysisk plan, på samme måte som tradisjonelle FPGA. Men i stedet for å hente inn én konfigurasjon i det den fyres opp for første gang, henter brikken inn åtte ulike konfigurasjoner, som den bytter mellom like fort som den interne klokken slår. Resultatet er at man får en brikke med logikk i åtte etasjer, selv om man bare har fysiske komponenter i én etasje. Konfigurasjonene avløser hverandre i samme rekkefølge hele tiden, og det finnes ordninger som sørger for at signaler kan sendes oppover til neste etasje. Når åttende etasje skal avløses, går signalene til første.

Den interne klokkefrekvensen til Tabulas brikke er 1,6 gigahertz. Siden det tar åtte klokkeslag å bevege seg gjennom alle etasjene, framstår den som en tredimensjonal brikke med en klokkefrekvens på 200 megahertz.

Tabula kaller produktkategorien de opererer med for 3PLD, en sammenstilling av «3D» og PLD. De kaller teknologien de har utviklet – og som er dekket av 150 patentsøknader, hvorav 80 er innvilget – for «Spacetime» («romtid»), siden den bygger på matematisk teori skapt av polsk-tyske Hermann Minkowski (1864–1909) for å behandle tid som en dimensjon på linje med høyde, bredde og dybde. Minkowski tok utgangspunkt i Albert Einsteins spesielle relativitetsteori, fra 1905. Selve brikken har fått navnet Abax, en slags forkortelse av «abakus», det vil si regnebrett eller kuleramme.

Det er hittil kunngjort fem ulike Abax-brikker. Forskjellen mellom dem er antall logiske porter. Alle har samme antall virtuelle etasjer og kjører i samme klokkefrekvens. Prisen varierer fra 105 til 200 dollar per enhet, i bestillinger på over 2000. Til utviklingsformål kan det kjøpes én og én brikke, til 500 dollar. Brikkene skal framstilles av taiwanske TSMC i en 40 nanometers prosess, som er den tetteste prosessen brukt for FPGA i dag.

Abax-brikkene konkurrerer først og fremst mot tradisjonelle FPGA. Dette markedet domineres globalt av to aktører, Altera og Xilinx, som til sammen har 90 prosent av markedet.

Fordelene som Tabula påberoper seg er ytelse per pris, en evne til å bygge funksjonsrike brikker på linje med dem de utfordrer, og muligheten som Spacetime gir til større fleksibilitet i valget mellom ytelse og funksjonalitet.

Prismessig tjener Tabula stort på den virtuelle konstruksjonen, siden brikkene kan gjøres langt mindre når tallet på disponible logiske porter er åtte ganger større enn det som må realiseres i silisium, og areal per brikke er faktoren som avgjør hvor mye det koster å framstille hver brikke. Siden Spacetime krever plass til sin egen logikk, er gevinsten langt fra den teoretiske åttegangeren. Beregninger fra Tabula konkluderer med at en Abax kan tilby 2,8 ganger mer logikk, 3,2 ganger mer brukerminne og 3 ganger så mange minneporter som en vanlig FPGA med samme areal og følgelig tilsvarende produksjonspris.

En annen fordel Tabula påberoper seg en ny mulighet til å balansere ytelse mot funksjonsriksom. Har man en anvendelse som løses best med en klokkefrekvens på 400 megahertz framfor 200, kan man med Spacetime velge å redusere antallet virtuelle etasjer i Abax-brikken fra åtte til fire. Siden man da bare får halvparten så mange logiske porter til disposisjon, må funksjonsrikdommen følgelig begrenses. Men dette er et valg som andre leverandører bare kan tilby gjennom ulike brikker.

Den praktiske klokkefrekvensen for de fleste FPGA ligger i dag på 200 til 350 megahertz. De raskeste når opptil 600 megahertz. Ved å kutte antall virtuelle etasjer til to, vil en Abax kunne kjøres i 800 megahertz.

Noe av den største utfordringen til Tabula er å framstille en kompilator og et utviklerverktøy som skjuler hele den sinnrike tidsdelingen, og lar utvikleren bygge opp applikasjonen som om den skulle foregå i en vanlig FPGA. Det er her matematikken til Minkowski kommer inn: Kompilatoren må sørge for at koplingene definert i to dimensjoner må realiseres effektivt i tre, og det er Minkowskis likninger som gjør det mulig å spille på tid som en vanlig dimensjon.

Microprocessor Report skriver at Tabula har en stor utfordring i konkurrentenes planlagte overgang til 28 nanometers produksjonsprosess, som vil kunne redusere Abax-brikkens pris/ytelse-fordel. Derfor betraktes det som avgjørende at Tabula selv lykkes i å framstille en Spacetime-basert brikke i 28 nanometer. En slik overgang vil gjøre det mulig med flere virtuelle etasjer og enda høyere klokkefrekvens. I så fall vil Tabula kunne øke sitt forsprang ytterligere.

En annen utfordring ligger i muligheten for at en konkurrent dukker opp med en effektiv løsning for å produsere programmerbare brikker i tre fysiske dimensjoner. Et av Tabulas mulige svar, er at de i så fall er beredt til å øke til fire dimensjoner. Det grunnleggende matematiske arbeidet for dette skal allerede være gjort.

Materiale som Tabula selv har lagt ut på nett, forteller hvordan de i første omgang vil konsentrere sitt salgsarbeid overfor produsenter av tele- og nettverksutstyr. De går blant annet gjennom ulike scenarioer der slikt utstyr enkelt kan oppgraderes ved å reprogrammere Abax-prosessorer.